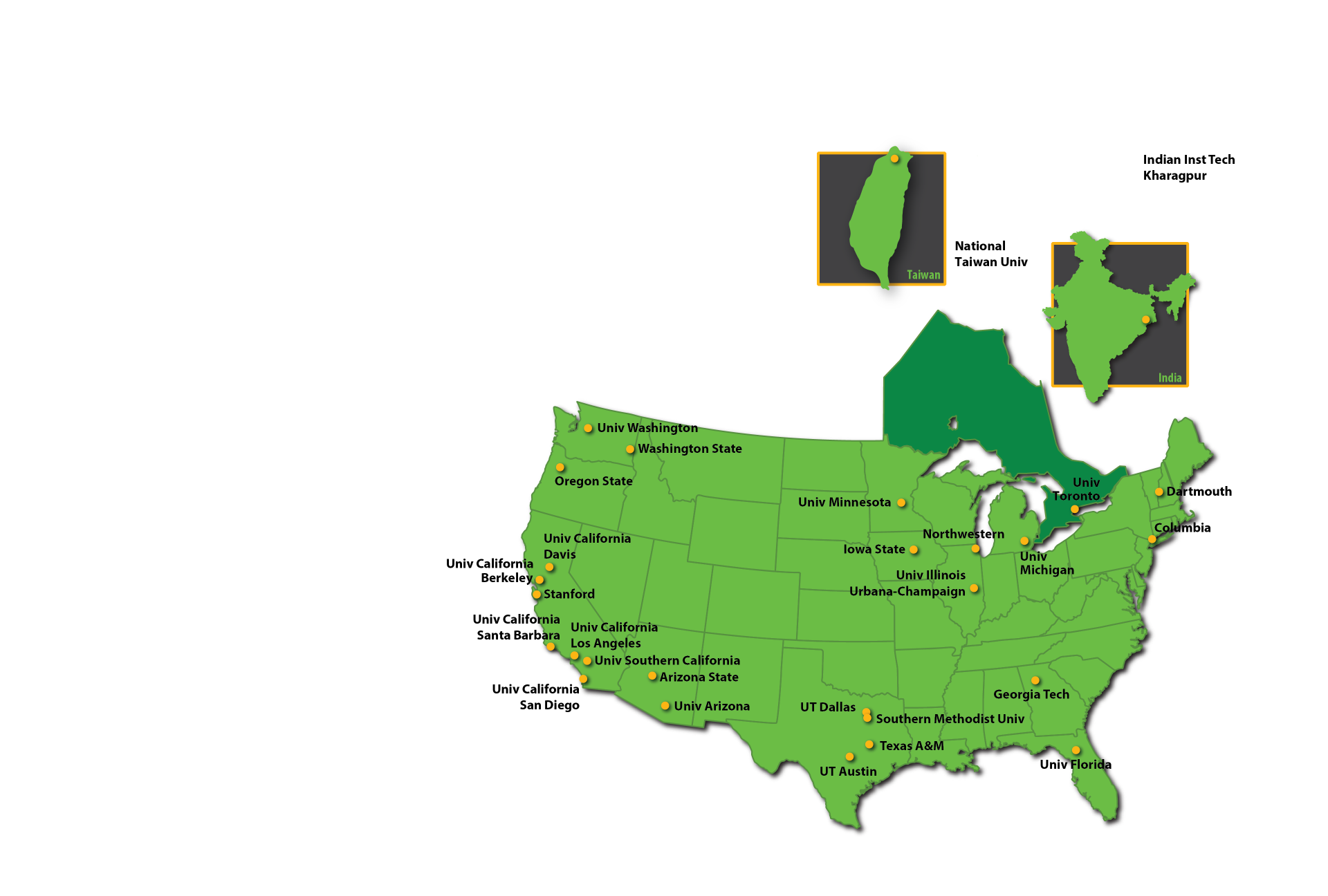

The Texas Analog Center of Excellence supported by the Global Research Collaboration (GRC) of Semiconductor Research Corporation seeks to transform analog, mixed signal, RF and power circuit research into a holistic collaborative process that creates a revolutionary integrated circuits and systems driven by both great societal needs and industry.